| Conversão de isolamento diferencial interno |  |

| Resolução: 16 bits | |

| Saída de trava de três estados | |

| Acompanhamento ininterrupto durante a transferência de dados | |

| pacote de metal de 32 fios |

HSDC/HRDC1746 série synchro/resolver para conversor digital é projetado | no princípio do princípio de rastreamento servo tipo II e adota | |||||

entrada de isolamento diferencial, a saída de dados adota trava de três estados | modo, é adequado para conversão de sinal analógico/sinal digital de | sincronizador de três fios e resolver de quatro fios. Com velocidade de conversão rápida | e desempenho estável e confiável, este dispositivo pode ser amplamente aplicado em medição de ângulo e sistema de controle automático. | Este produto é feito pelo processo de integração híbrida de filme espesso e é | ||

Pacote de metal totalmente selado DIP de 32 fios. Tanto o desenho como | ||||||

fabricação do produto satisfaz os requisitos de GJB2438A-2002 | “Especificação geral para circuitos integrados híbridos” e | especificações do produto. | ||||

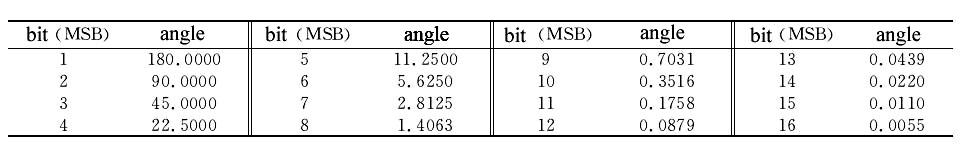

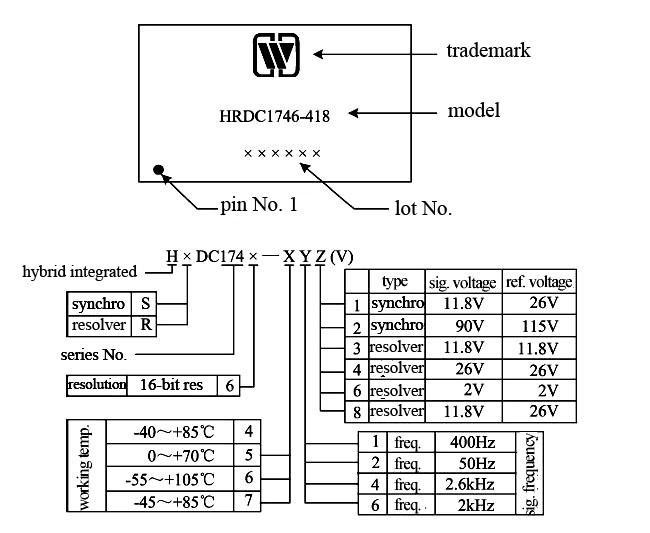

4. Desempenho elétrico (Tabela 2, Tabela 3) | Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1746) | Tabela 2 Condições nominais e condições operacionais recomendadas | Tabela 3 Características elétricas | Máximo absoluto Valor nominal | ||

Tensão de alimentação Vs: ± 17,25VDC | Parâmetro | -3 | 3 | |||

HSDC/HRDC | Série 1746 | 16 | ||||

Notas | Tensão de alimentação lógica VL: +7V | 50 | Faixa de temperatura de armazenamento: -55 ℃ ~ 150 ℃ | |||

Min. | Máx. | 2 | 90 | |||

Condições de operação recomendadas | Tensão de alimentação Vs: ± 15 ± 5% | 2 | Precisão/minuto angular | |||

| 2,6 mil |  |

| Mudança de fase entre sinal e excitação:<±10% Tensão do sinal (valor efetivo)/V Faixa de temperatura operacional (TA): -40~+105℃  | |

| Tensão de referência (valor efetivo)/V | 115 |

| |

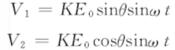

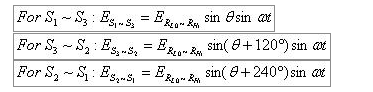

| uma função de erro é obtida: |

Através da amplificação do erro, discriminação de fase e filtragem desteof função de erro, sin(θ-φ) é obtido, quando θ-φu003d0 (dentro da precisão | do conversor), este erro fará com que a tensão controladaofpulso de correção de saída do oscilador para alterar o ângulo digital binário φ |

| |

| do contador reversível de modo a tornar o valor φ de saída igual ao | entrada θ dentro da precisão do conversor, o sistema torna-se estável |

| e pode rastrear a mudança do ângulo de entrada φ. Desta forma, um binário digital | |

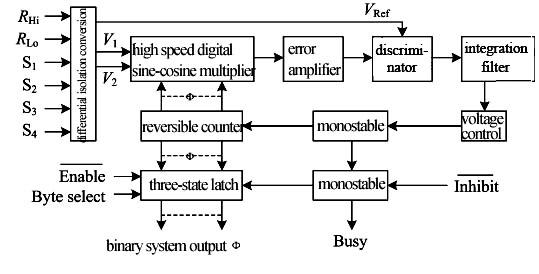

contador reversível (Fig. 2). | Fig. 2 Diagrama de blocos do circuito | (1) Características dinâmicas | A função de transferência do conversor é mostrada na Fig. 3: | Ganho em malha aberta: | Função de circuito fechado: |

1 | NC | Para o módulo deste modelo Kau003d48000/S2, T1u003d7,1ms, T2u003d1,25ms | 17 | NC | Fig. 3 Transferência de função do conversor |

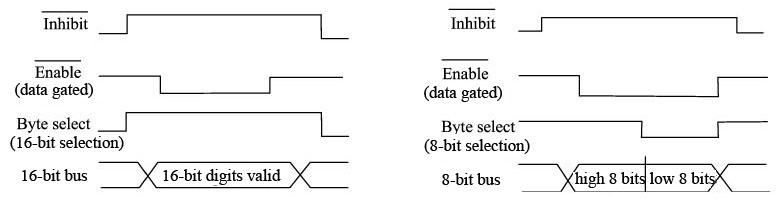

2 | D9 | (2) Métodos de transferência de dados e sequência de tempo | 18 | Controle de seleção de chip Ativar | Este pino é o pino de entrada da lógica de controle, sua função é a saída |

3 | dados para o conversor para realizar o controle de três estados. O nível baixo é | válido, os dados de saída do conversor ocupam o barramento de dados. Quando é em | 19 | alto nível, o pino de saída de dados do conversor está em três estados, o | dispositivo não ocupa o barramento. |

4 | Seleção de bytes | Este pino é o pino de entrada de controle, sua função é executar externamente | 20 | controle de seleção nos dados de saída do conversor na transferência | modo de barramento de dados de 8 bits ou barramento de dados de 16 bits. Quando a transferência de barramento de dados de 16 bits |

5 | for necessário, mantenha este pino lógico alto, os dados serão | transferido no barramento, a saída de byte alto está no pino D1 a D8 (D1 é | 21 | bit alto) e o byte baixo está em D9 a D16. Quando a transferência de barramento de dados de 8 bits | for necessário, os dados são obtidos nos pinos D1 a D8 (dispostos de alto |

6 | para baixo), e 8 bits altos e 8 bits baixos são obtidos através de duas | seqüências, em outras palavras, quando Byte select é lógico alto, alto 8 bits | 22 | são emitidos e quando é lógico baixo, 8 bits baixos são emitidos. | Controle de bloqueio de dados (sinal de inibição) Inibição |

7 | Este pino é o pino de entrada da lógica de controle, sua função é a saída | dados externamente ao conversor para realizar travamento ou desvio opcional | 23 | ao controle. Em alto nível, os dados de saída do conversor são diretamente | saída sem travamento, veja o diagrama de seqüência de tempo dos dados |

8 | transferir. Em nível baixo, os dados de saída do conversor são travados, o | loop interno não é interrompido e o rastreamento continua funcionando durante todo o | 24 | D1 | tempo, mas o contador não emite dados. Quando é necessário transferir |

9 | dados, o conversor primeiro faz o sinal de controle de inibição para bloquear os dados de alto para baixo, mantém a lógica baixa por 640ns, então define a entrada de habilitar para baixo (neste momento o dispositivo ocupa o barramento de dados) e então | obtém os dados através da seleção de Byte, então gire todas as lógicas de controle para alto | 25 | D2 | para atualizar e travar os dados para se preparar para a transferência do |

10 | próximos dados, consulte os diagramas de seqüência de tempo de transferência de dados Fig.4 | e Fig.5. | 26 | D3 | (3) Método de atenuação do sinal de entrada (Fig.4 e Fig.5) |

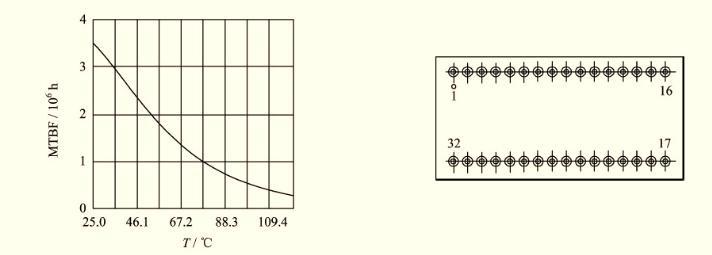

11 | Fig 4 Sequência de tempo de transferência de barramento de 16 bits | Fig5 Sequência de tempo de transferência de barramento de 8 bits | 27 | D4 | 6. Curva MTBF (Fig. 6) |

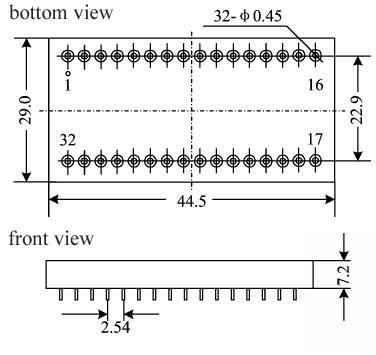

12 | Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1746) | 7. Designação do pino (Fig.7, Tabela 4) | 28 | D5 | Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1746) |

13 | S3 | Fig.6 Curva de temperatura MTBF | 29 | D6 | Fig.7 Designação do pino (Vista inferior) |

14 | S2 | (Nota: conforme GJB/Z299B-98, bom estado do solo previsto) | 30 | D7 | Tabela 4 Descrição funcional dos terminais de chumbo |

15 | S1 | Alfinete | 31 | D7 | Símbolo |

16 | NC | Significado | 32 | NC | Alfinete |

Terra | D12 | Saída digital para 12 bits | -VS | -fonte de alimentação de 15V | D13 | Saída digital para 13 bits | + VS | +15V fonte de alimentação |

D14 | Saída digital para 14 bits | Ni | Inibir | Ni | Controle de bloqueio de dados | D15 | Saída digital para 15 bits |

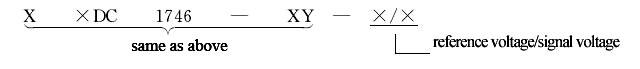

X

X