| Frequência de excitação 50Hz, 400Hz e 2,6kHz |  |

| Resolução: 10 bits, 12 bits, 14 bits | |

| Alta velocidade de rastreamento | |

| A entrada não padrão é ajustável através de resistência externa ou ajustada no terminal de entrada do produto | |

| Saída de tensão DC diretamente proporcional à velocidade angular | |

| Compatível com a série SDC1700 da empresa americana AD |

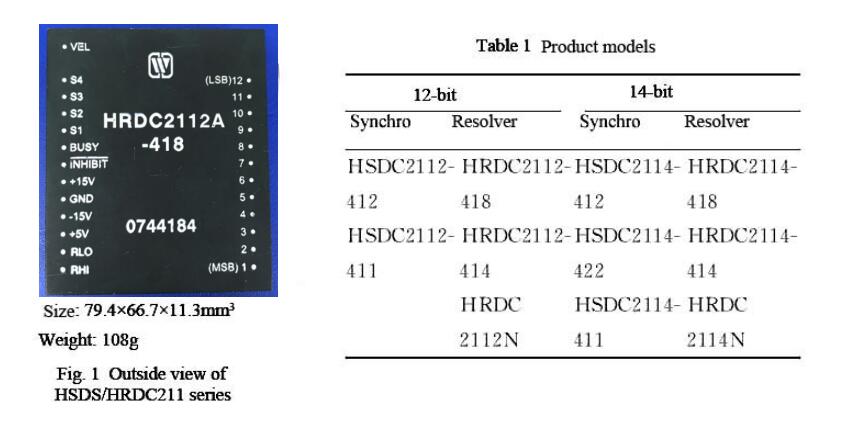

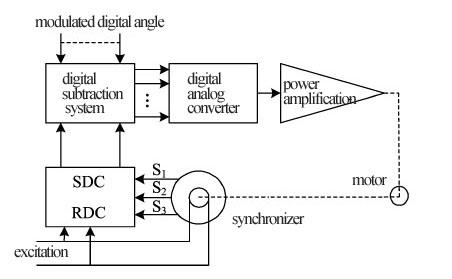

conversão. | A potência de operação é de ±15V e + 5V DC. Existem dois tipos de |

sinal de saída: sincronização de três linhas e sinal de referência (conversor SDC) | |

ou resolvedor de quatro linhas e sinal de referência (conversor RDC); a saída | |

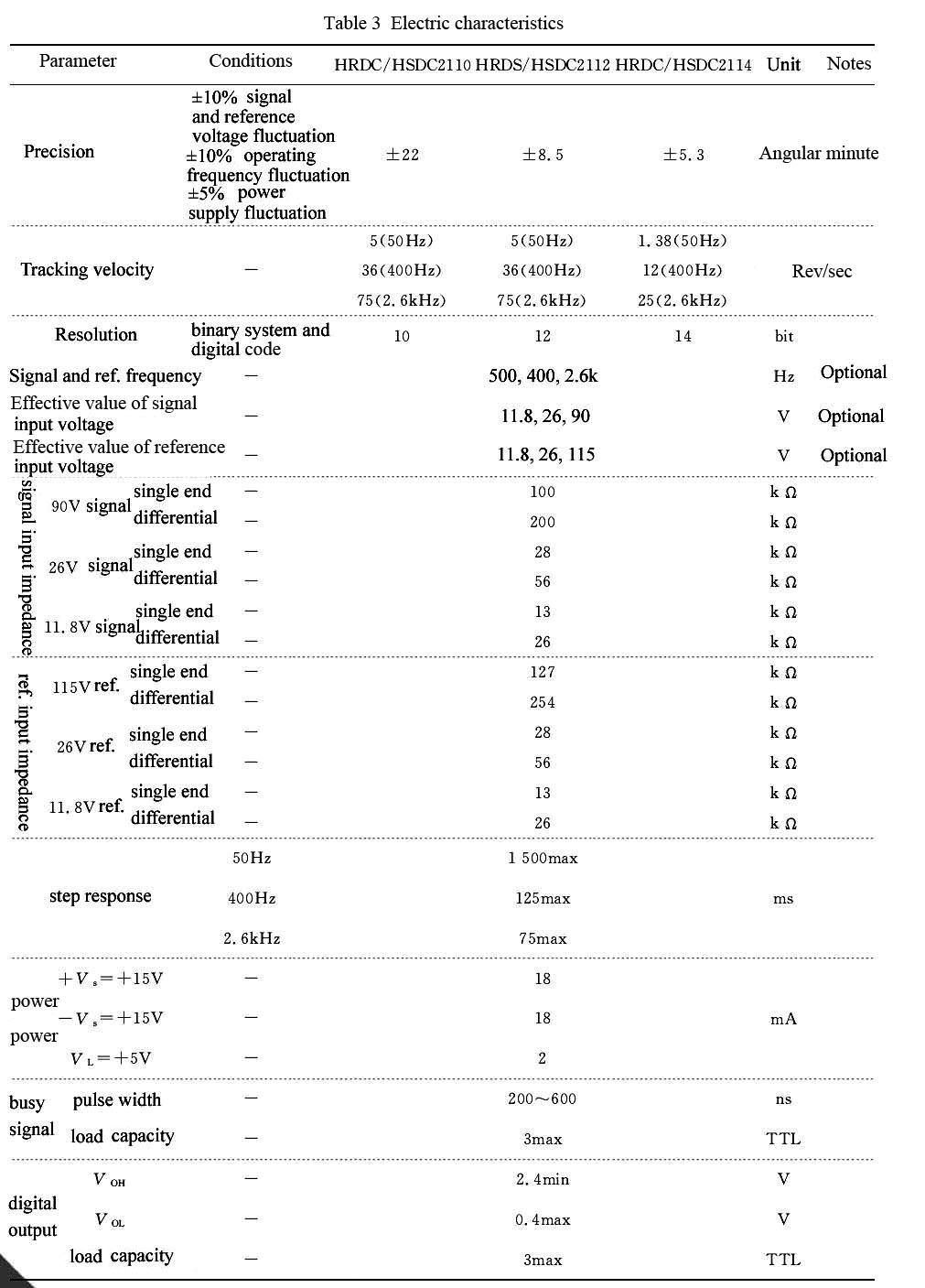

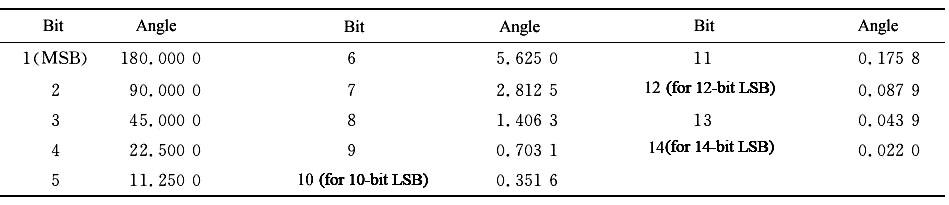

são códigos digitais paralelos do sistema binário. | 4 Desempenho elétrico (Tabela 2, Tabela 3) de Sincronização para |

Conversores digitais ou Resolver para conversores digitais (HSDC/HRDC211 | |

Series) | |

Tabela 2 Condições nominais e condições operacionais recomendadas | |

Máximo absoluto Valor nominal | |

Tensão de alimentação Vs: ± 17,5V |

| Valor efetivo da tensão de referência VRef: 11,8V, 26V, 115V Valor efetivo da tensão de referência V1*: 11,8V, 26V, 90V |  Frequência de referência f*: 50Hz, 400Hz, 2,6kHz |

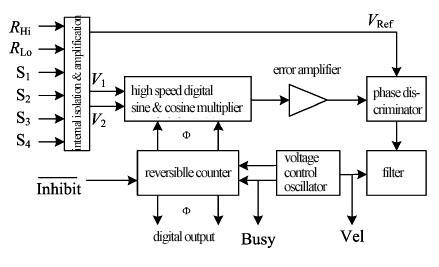

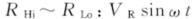

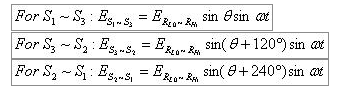

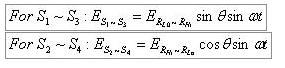

Onde, θ é o ângulo de entrada analógica O sinal ortogonal é multiplicado pelo ângulo digital binário φ no O sinal ortogonal é multiplicado pelo ângulo digital binário φ no | contador reversível interno no multiplicador da função seno-cosseno e |

θ-φ≠0, o oscilador controlado por tensão produzirá pulso para alterar o | dados no contador reversível, até que θ-φ se torne zero dentro do |

|  |

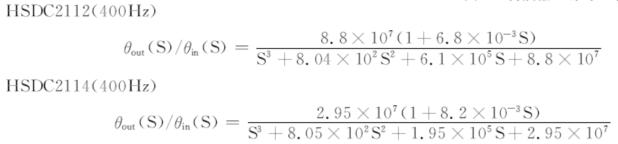

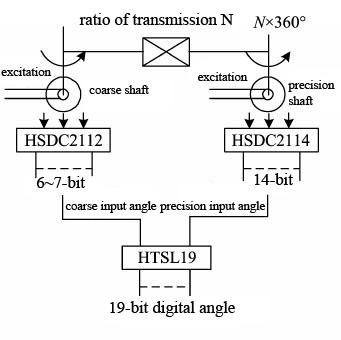

| precisão do conversor, durante este processo, o conversor rastreia o mudança do ângulo de entrada θ o tempo todo. Para o princípio de funcionamento, veja a Fig. | 2. Função de transferência: a seguir estão os parâmetros para a função de transferência de HSDC2112 e HSDC2114(400Hz), para outros modelos, entre em contato com o fabricante diretamente. Fig.2 Diagrama de blocos para princípio de operação do conversor |

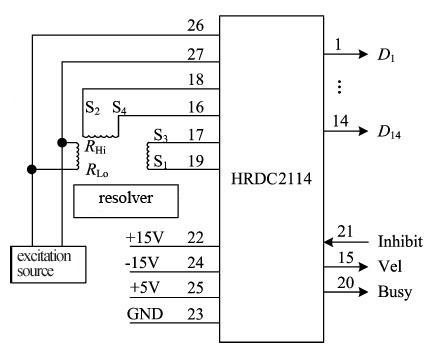

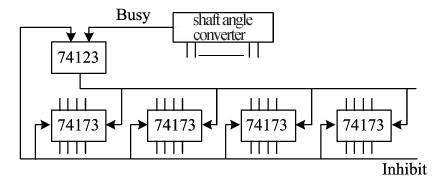

Existem dois métodos para ler os dados válidos do conversor da seguinte forma: | Método de inibição (leitura síncrona): | Defina Inibir como lógico "0", neste momento, o conversor interromperá o rastreamento. Esperar por | 1μs até que os dados de saída estejam estáveis, leia os dados, os dados lidos são os | um válido neste momento (1μs foi atrasado). Defina como lógico "1", neste momento, o conversor começará a rastrear novamente para se preparar para ler os próximos dados válidos. | Método ocupado (leitura assíncrona): Inibir |

1 | D1 | No modo de leitura assíncrona, | 15 | é definido como lógico “1” ou vago, se o loop interno estiver sempre em estável | estado ou se os dados de saída são válidos deve ser determinado através do |

2 | D2 | estado do sinal de ocupado Ocupado. Quando o sinal de ocupado está em nível alto, ele | 16 | S4 | indica que os dados estão sendo convertidos e os dados neste momento são |

3 | D3 | instável e inválido; quando o sinal de ocupado está em nível baixo, indica o | 17 | S3 | a conversão de dados foi concluída e os dados neste momento estão estáveis |

4 | D4 | e válido. No modo de leitura assíncrona, a saída Ocupado é um trem de pulso de | 18 | S2 | No nível TTL, a largura entre eles está relacionada à velocidade de rotação. Referir-se |

5 | D5 | diagrama de seqüência de tempo de transferência de dados Fig. 3. | 19 | S1 | Fig.3 Sequência de tempo de transferência de dados |

6 | D6 | (2) Método de atenuação do sinal de entrada | 20 | Se o sincronizador ou resolvedor usado pelo usuário não for padrão, para | fazer com que a tensão do sinal de entrada e a tensão de excitação de entrada correspondam à |

7 | D7 | valores nominais do conversor, o usuário pode adotar o método de | 21 |

| resistência de atenuação externa conectada em série, ou seja, para cada 1V |

8 | D8 | excedendo o valor nominal, conecte a resistência de 1,1kΩ em série no | 22 | terminal de entrada correspondente. Ao usar o conversor, a série | resistência em cada terminal deve ser precisamente selecionada e fornecida, |

9 | D9 | e materiais de resistência do mesmo lote devem ser adotados de forma a garantir | 23 | a precisão de conversão do conversor dentro da ampla temperatura | intervalo, para cada 0,1% o erro de correspondência da resistência em série será |

10 | gerar 1,7 erro de conversão de minuto angular. | É recomendado pelo fabricante que é preferível notificar | 24 | o fabricante para personalizar o sincronizador ou resolver não padrão conforme | de acordo com os parâmetros necessários quando o usuário os usa. |

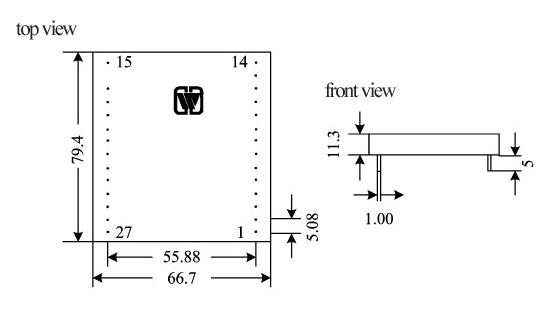

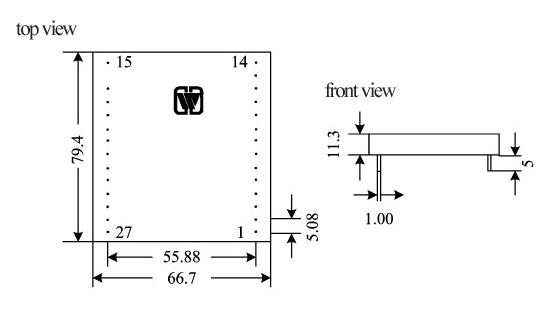

11 | 6 Curva MTBF (Fig. 4) de Conversores Sincro para Digital ou Resolver para Conversores Digitais (Série HSDC/HRDC211) | Designação de 7 pinos (Fig. 5, Tabela 4) de Conversores Sincro para Digital ou Resolver para Conversores Digitais (Série HSDC/HRDC211) | 25 | Fig. 4 Curva de temperatura MTBF | (Nota: de acordo com GJB/Z299B-98, boas condições de solo previstas) |

12 | Notas: | ① a estrutura acima é adequada para HRDC2114 | 26 | ② para SDC, sem pino S4 | ③ para dispositivo de 12 bits, sem pinos 13 e 14, para dispositivo de 10 bits, sem pinos 11, 12, 13 e 14. |

13 | Fig.5 Designação do pino (vista superior) | Tabela 4 Designação do pino | 27 | Alfinete | Símbolo |

14 | Função | Alfinete |

| Entrada de sinal Saída digital de bit 6 Ocupado Entrada de sinal ocupado |  |

| Saída digital de bit 7 |

| -15V |  - Fonte de alimentação de 15V |

D11 |

|  |

| Fonte de alimentação +5V | D12 |

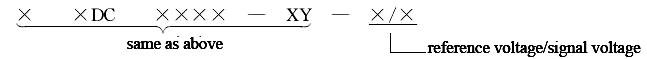

X

X