| Alta precisão |  |

| Tamanho pequeno | |

| Alta velocidade de rastreamento | |

| Acompanhamento ininterrupto durante a transferência de dados | |

| Saída de trava de três estados | |

| Baixo consumo de energia |

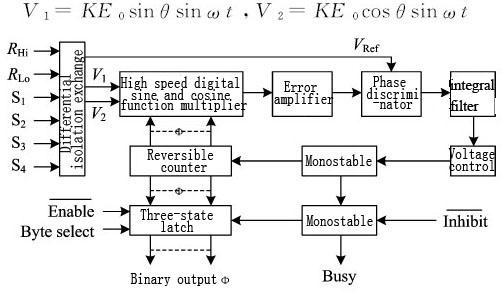

sinal de saída é um código binário natural paralelo armazenado em buffer | trinco de três estados e compatível com o nível TTL. |

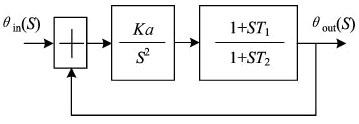

O produto aplica circuito servo de segunda ordem com tamanho pequeno e leve | |

peso, e o usuário pode usá-lo de maneira muito conveniente controlando | |

pinos de sinal. | |

Tabela 2 Condições nominais e condições operacionais recomendadas | Máx. valor de classificação absoluto |

Tensão de alimentação +VS: 12,5~17,5V | |

Tensão de alimentação -VS: -17,5~-12,5V | |

Tensão lógica VL: 7V | |

Faixa de temperatura de armazenamento: -40~+100℃ | |

Condições de operação recomendadas |

Tensão de referência (valor efetivo) VRef: valor nominal ±10% | Tensão do sinal (valor efetivo) V1*: valor nominal ±10% Frequência de referência f*: valor nominal ±10% | Faixa de temperatura operacional TA: -40~+85℃ | Nota: * indica que pode ser personalizado conforme a necessidade do usuário. | |

Tabela 2 Características elétricas | Parâmetro | |||

Condições (-40~+85℃) | (Salvo indicação em contrário) | 12 | 16 | (série MSDC/MRDC37) |

Unidade | – | 3 | 36 | Min. |

Máx. | Resolução/RES | Faixa de 0~360º | – | V |

Pedaço | Velocidade de rastreamento/St① | – | rps | V |

Alto nível de saída/VOH | TAu003d25℃ | – | 2.4 | W |

Baixo nível de saída/VOL | TAu003d25℃ | – | 0,8 | % |

Consumo de energia/PD | – | 2 | TAu003d25℃ | V |

1.3 | – | 2 | 90 | V |

Vel linearidade/ERl | – | 30 | TAu003d25℃ | Hz |

1,0 | – | ±3 | Faixa de tensão de referência | 115 |

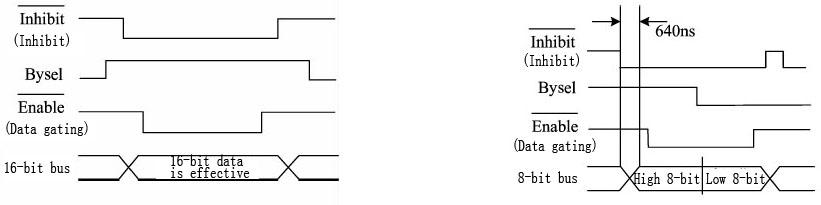

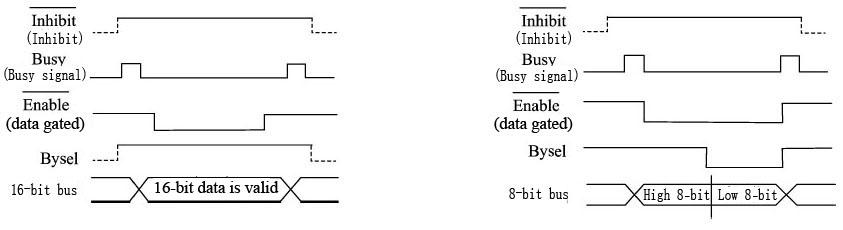

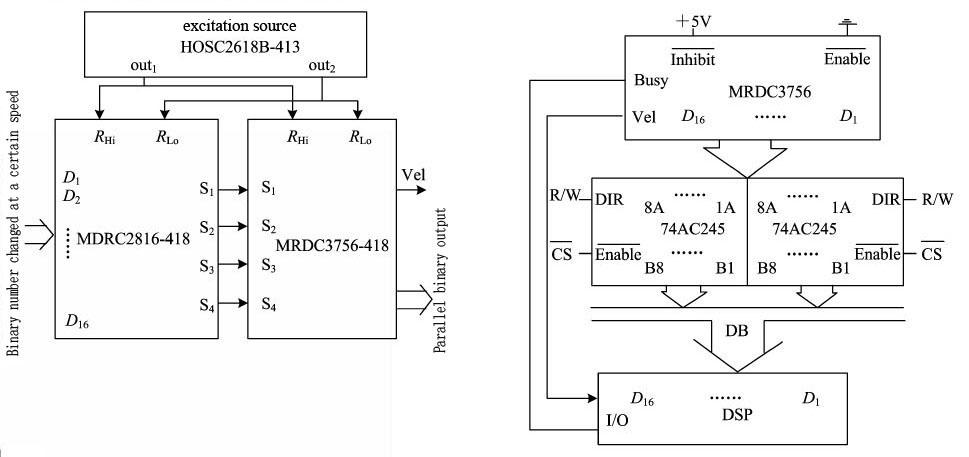

B: o conversor está conectado ao barramento de 8 bits, o bit D1~D8 está conectado ao barramento de dados e o restante está vazio. | Defina a inibição da lógica 1 para a lógica 0 (bloqueio de dados) e aguarde 1μs; defina Enable para 0 lógico para permitir que o latch no conversor envie dados; definir | Bysel para lógica 1, leia diretamente os dados altos de 8 bits, defina Bysel para | lógica 0, leia os dados em outros bits com preenchimento automático de zero em | os bits vagos; defina para lógica 1 para se preparar para ler os próximos dados efetivos (Fig. 5). | Inibir | Fig4 Sequência de tempo de transferência de barramento de 16 bits Fig5 Sequência de tempo de transferência de barramento de 8 bits | (2) Método ocupado (leitura assíncrona): | No modo de leitura assíncrona, é definido Inibir como lógico 1 ou vazio, independentemente de o loop interno estar sempre no |

1 | D1 | estado estável ou se os dados de saída são válidos deve ser determinado | 13 | através do status do sinal de ocupado Ocupado. Quando o sinal de ocupado está alto | nível, indica que os dados estão sendo convertidos e os dados neste | 25 | o tempo é instável e inválido; quando o sinal de ocupado está em nível baixo, | indica que a conversão de dados foi concluída e os dados neste |

2 | D2 | o tempo é estável e válido. Uma vez que o nível alto ocorre em Ocupado durante a leitura, | 14 | a leitura neste momento é inválida. No modo de leitura assíncrona, o | A saída ocupada é um trem de pulso de nível TTL, sua largura depende de sua | 26 | velocidade de rotação, também existem dois métodos de uso do barramento, ou seja, 8 bits | e 16 bits, a leitura de dados durante a saída de dados efetiva também é |

3 | D3 | controlado por Enable , consulte o diagrama de seqüência de tempo para transferência de dados (Fig. 6 e Fig. 7). | 15 | Fig.6 Diagrama de seqüência de tempo para transferência de barramento de 16 bits Fig.7 Diagrama de seqüência de tempo para transferência de barramento de 8 bits | Pinos de sinal de status: Ocupado, DIR, R, C. | 27 | Quando a entrada do conversor muda, Busy emite um trem de pulsos | do nível CMOS, sua frequência é determinada pela maior rotação |

4 | D4 | Rapidez. Quando ocupado está em alto nível, significa que o servo de segunda ordem | 16 | circuito no conversor está operando, os dados na extremidade de saída digital são | mudando; pelo contrário, o computador pode ler diretamente os dados. | 28 | O sinal DIR é usado para indicar rotação para frente/para trás. Quando a saída | |

5 | D5 | o código está em contagem crescente, a saída é de alto nível; quando o código de saída é | 17 | NC | contagem regressiva, a saída é de baixo nível. | 29 | Saída de sinal zero R.C: quando os dados de saída aumentam de 1 para | tudo 0, ou os dados de saída decrementam de tudo 0 para tudo 1, o |

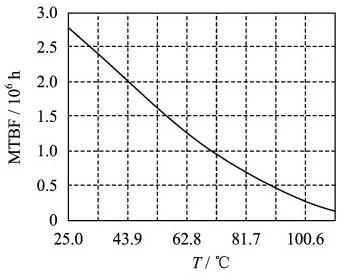

6 | D6 | saída é pulso positivo, a largura do pulso é 200μs. | 18 | 5. Curva MTBF de conversores sincronizados para digitais ou resolvedor para conversores digitais (série MSDC/MRDC37) (Fig. 7) | Fig. 8 Curva de temperatura MTBF | 30 | (Nota: conforme GJB/Z299B-98, bom estado do solo previsto) | |

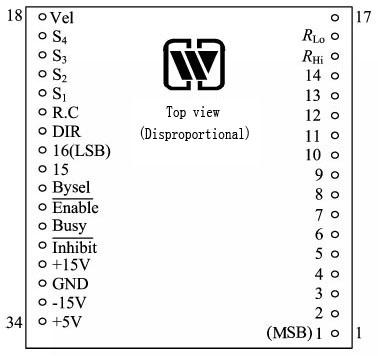

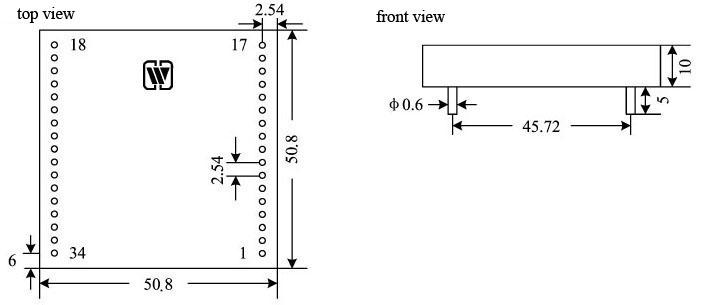

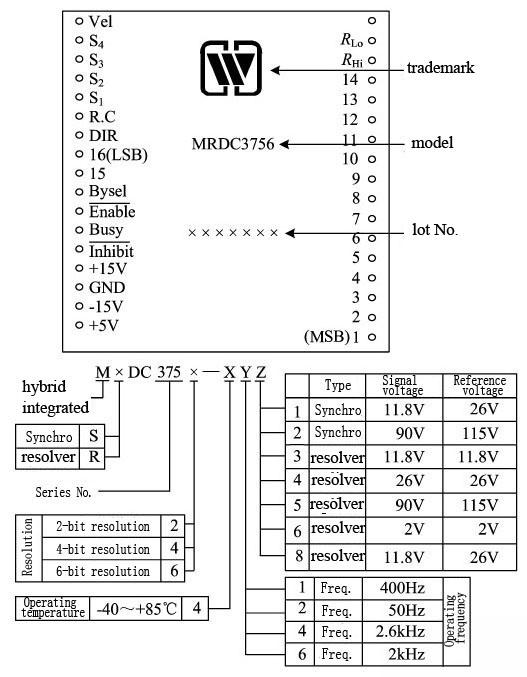

7 | D7 | 6. Designação do pino de conversores sincronizados para digitais ou resolvedores para conversores digitais (série MSDC/MRDC37) (Fig. 9, Tabela 3) | 19 | S4 | Fig.9 Designação do pino (vista superior) | 31 | Tabela 3 Designação do pino | Alfinete |

8 | D8 | Símbolo | 20 | S3 | Significado | 32 | Alfinete | Símbolo |

9 | D9 | Significado | 21 | S2 | Alfinete | 33 | Símbolo | Significado |

10 | Saída digital 1 (bit mais alto) | D13 | 22 | S1 | Saída digital 13 | 34 | VL | D16 |

11 | Saída digital 16 | Saída digital 2 | 23 | D14 | Saída digital 14 | |||

12 | D15 | Saída digital 15 | 24 | Saída digital 3 | RHi |

Entrada de sinal de referência (low end) | Ativar sinal | Saída digital 5 | Fim da linha | Ocupado | Sinal ocupado |

Saída digital 6 | Vel | 7 | Saída de tensão de velocidade | 13 | Sinal de inibição |

2 | Saída digital 7 | 8 | Entrada de sinal | 14 | +V |

3 | Fonte de alimentação +15V | 9 | Saída digital 8 | 15 | Entrada de sinal |

4 | GND | 10 | Aterramento de energia | 16 | Saída digital 9 |

5 | Entrada de sinal | 11 | -Vs | ||

6 | - Fonte de alimentação de 15V | 12 | D10 |

| |

| Entrada de sinal | Fonte de alimentação +5V |

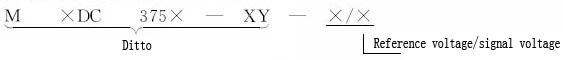

X

X