| Conversão de isolamento diferencial interno |  |

| Resolução de 16 bits | |

| Precisão: 2 minutos angulares | |

| Saída de trava de três estados | |

| Alta velocidade de rastreamento contínuo | |

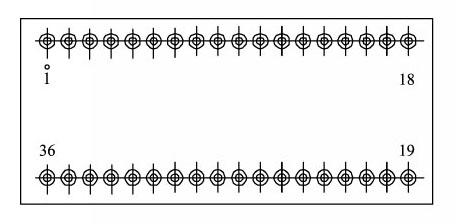

| Pacote DDIP resistente a neblina de salino de 36 fios | |

| Pin-to-Pin compatível com Modelo SDC14560 da DDC empresa |

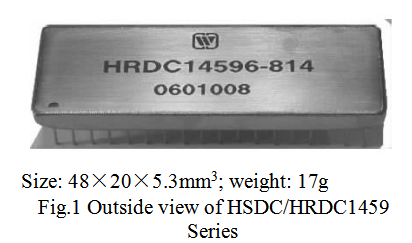

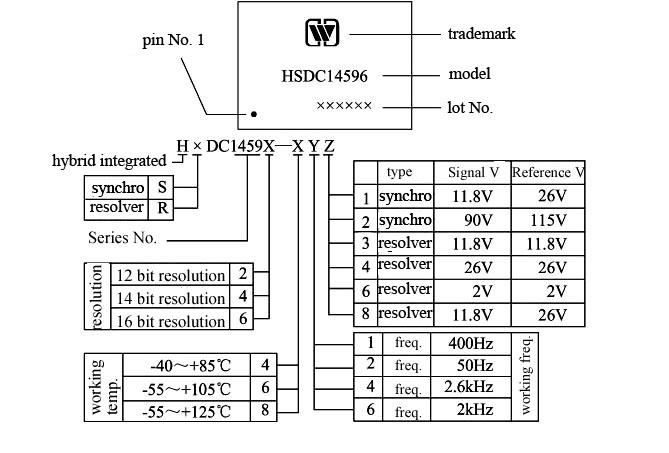

| dispositivo de conversão integrado para rastreamento contínuo projetado no | princípio do servo modelo II. Os produtos desta série são projetados e |

| fabricado pelo processo MCM, os elementos principais adotam chip especial | |

| desenvolvido de forma independente pelo nosso instituto. A disposição dos pinos é | |

| compatível com produtos da série SDC14560 da empresa americana DDC, 16 bits | |

| saída de trava de dados de código binário natural paralelo, DIP de 36 linhas totalmente | |

| pacote de metal selado, tem as vantagens de alta precisão, pequeno | |

| volume, baixo consumo de energia, peso leve e alta confiabilidade etc., | e pode ser amplamente utilizado em importantes armas estratégicas e táticas, como |

| aeronave, embarcação naval, canhão, míssil, radar, tanque, etc. | |

| 4. Desempenho elétrico (Tabela 1, Tabela 2) | |

| Sincronizar para conversores digitais ou resolver para conversores digitais (série HSDC/HRDC1459) | |

| Tabela 1 Condições nominais e condições operacionais recomendadas | |

| Absoluto máx. Valor nominal |

| Tensão de sinal V1: valor classificado ±20% | Tensão de referência VRef: valor classificado ±20% | Frequência operacional f: valor classificado ±20% | |

| Temperatura de armazenamento Tstg: -65~150℃ | Condições de operação recomendadas | ||

| Tensão de alimentação lógica VL: 5±0,5V | Tensão de alimentação Vs: 15±0,75V | ||

| Tensão do sinal V1: valor nominal ± 10% | Tensão de referência VRef: valor classificado ±20% | Frequência operacional f: valor classificado ±20% | — |

| Faixa de temperatura de operação (TA): -55℃~125℃ | Nota: * indica que pode ser personalizado conforme a necessidade do usuário. | Tabela 2 Características elétricas | Parâmetro |

| Condições | — | Série HSDC14569 | (VSu003d15V, VLu003d+5V) |

| Padrão militar (Q/HW20725-2006) | — | 2V | Min. |

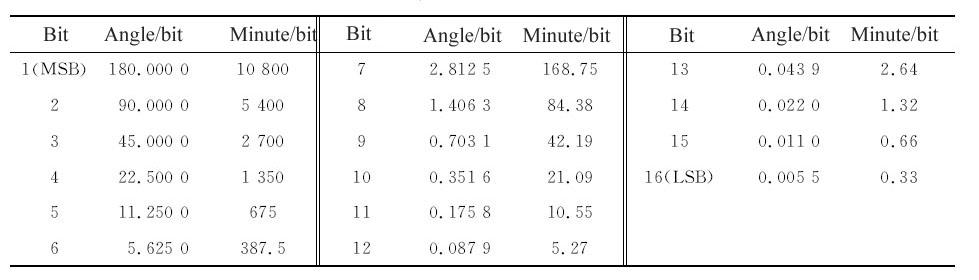

| Máx. | — | Resolução | Código digital paralelo do sistema binário |

| 16 bits | — | 2V | Precisão |

| ± 10% da tensão do sinal, tensão de referência e faixa de flutuação da frequência operacional | — | -2 minutos angulares | +2 minutos angulares |

| Faixa de frequência de referência | — | 50Hz | 2600Hz |

| Faixa de tensão de referência | — | 115V | Impedância de entrada de referência |

4,4kΩ 4,4kΩ | — | 0 | 129,2 kΩ |

Faixa de tensão do sinal Faixa de tensão do sinal | — | 0 | 90V |

Impedância de entrada de sinal Impedância de entrada de sinal | — | 0 | 4,4kΩ |

| 102,2 kΩ | — | Mudança de fase de sinal/referência | —70° |

| +70° | — | Nível lógico de entrada | Lógica "1" ≥3,3V |

| Lógica "0" ≤0,8V | — | entrada | 0,8 V |

| entrada | — | 0,8 V | |

| entrada | — | — | 0,8 V |

| Nível lógico de saída | — | — | Lógica "1" ≥3,3V |

| Lógica "0" ≤0,8V | — | — | Saída de código de ângulo digital |

| Lógica "1" ≥3,3V | — | — | Lógica "0" ≤0,8V |

| Convertendo a saída do sinal de ocupado (CB) | — | 200ns | 600ns |

| Saída de bits de detecção de falhas | Lógica "0" indica falha | — | Capacidade de carregamento |

| 3TTL | Velocidade de rastreamento | ||

| 2,5 rpm | Aceleração constante | ||

| +10V Atual VSu003d+15V 10mA |  VS u003d—15V |

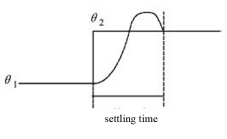

Rapidez. O processo de oscilação do ângulo digital de saída é mostrado na

Rapidez. O processo de oscilação do ângulo digital de saída é mostrado na 6. Princípio de funcionamento (Fig. 3)

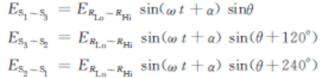

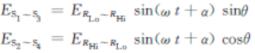

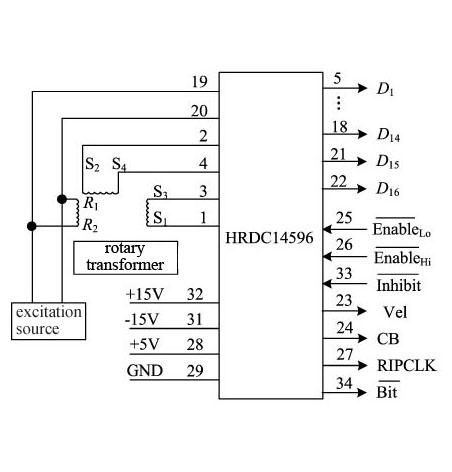

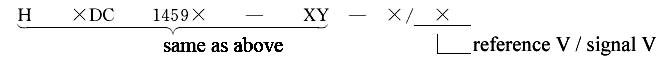

6. Princípio de funcionamento (Fig. 3)| Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1459) O sinal de sincro (ou resolver) é convertido no sinal ortogonal através do isolamento diferencial interno: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofOnde, θ é o ângulo de entrada analógica. Fig.2 Curva da etapa resposta | Esses dois sinais e o ângulo digital φ do contador reversível internoof são multiplicados no multiplicador das funções Seno e Cosseno e são erro tratado: |

| amplificação, discriminação de fase e filtragem de integração, se | θ-φ≠0, o oscilador controlado por tensão emitirá os pulsos e o | contagens reversíveis, até que θ-φ se torne zero dentro da precisão de | o conversor, durante este processo, a conversão acompanha a mudança de | ângulo de entrada o tempo todo. | Método de leitura: |

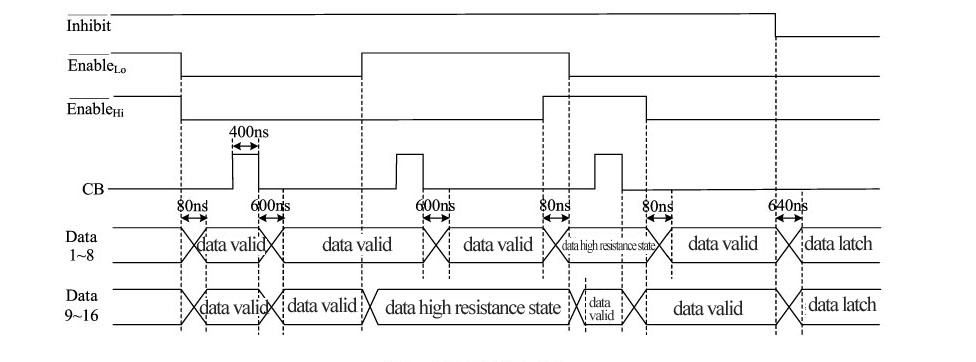

| 1 | S1 | Os dois métodos a seguir estão disponíveis para transferência de dados: | 25 |  | (1) Método de inibição: |

| 2 | S2 | Após 640ns de | 26 |  | lógico baixo, os dados de saída são válidos e o conversor realiza a transferência de dados através |

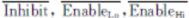

| 3 | S3 | e | 27 | . Após a liberação da Inibição, o sistema gerará automaticamente um pulso com largura igual ao pulso ocupado para atualização de dados. | (2) Modo de busto: |

| 4 | S4 | Na borda ascendente do pulso Ocupado, o contador reversível de três estados conta; na borda descendente do pulso Ocupado, ele gera internamente um pulso de trava com uma largura igual ao pulso Ocupado para atualizar os dados da trava de três estados, a sequência de tempo de transferência de dados é mostrada na Fig. 4, em outras palavras, após 600 ns de Lógica de ocupado baixo, a transferência estável de dados é válida. No modo de leitura assíncrona, a saída Ocupado é o trem de pulso nível CMOS. A largura de seu nível alto e baixo depende da frequência operacional e velocidade rotacional do dispositivo selecionado. | 28 | VL | Fig.4 Sequência de tempo de transferência de dados |

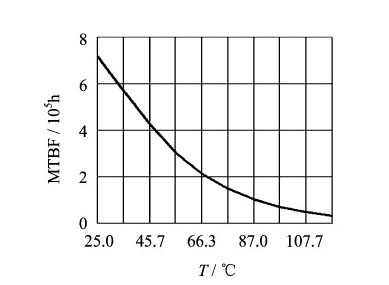

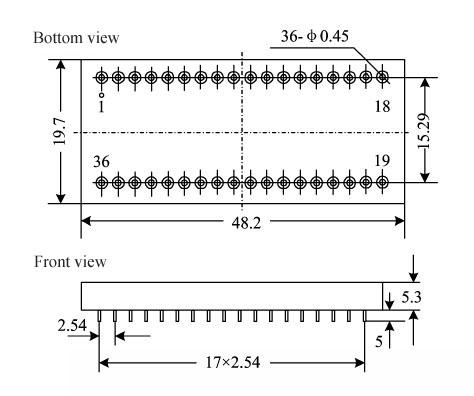

| 7. Curva MTBF (Fig.5) | Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1459) | Fig.5 Curva de temperatura MTBF | 29 | 8. Designação de pinos (Fig.6, Tabela 3) | Sincronizador para conversores digitais ou resolvedor para conversores digitais (série HSDC/HRDC1459) |

| 19 | Fig.6 Designação do pino (Vista inferior) | (Nota: de acordo com GJB/Z299B-98, boas condições de solo previstas) | 30 | NC | Tabela 3 Designação do pino |

| 20 | RL | Alfinete | 31 | Símbolo | Significado |

| 21 | Alfinete | Símbolo | 32 | VS | Significado |

| 22 | Entrada do resolvedor S1 (ou entrada sincronizada S1) | Controle habilitado digital de 8 bits inferiores | 33 | Entrada do resolvedor S2 (ou entrada sincronizada S2) | Controle habilitado digital de 8 bits superiores |

| 23 | Entrada do resolvedor S3 (ou entrada sincronizada S3) | RIPCLK | 34 | Saída de sinal zero bit | Entrada do resolvedor S4 (deixe desconectado) |

| 24 | CB | +5V fonte de alimentação | 5 de janeiro de 18 | NC | D1-D14 |

| Saída digital 1(MSB)-14 | GND |

| Terra | RHi |

| Entrada de sinal de referência de ponta | Sem conexão |

| RL | Entrada de sinal de referência de baixa extremidade |

-VS

-VS -Fonte de alimentação de 15V

-Fonte de alimentação de 15V

D15 Saída digital 15

Saída digital 15 ).

).

+15V Fonte de alimentação

D16

Saída digital 16 (LSB)

Inibir

Entrada de sinal estático

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Entrada de sinal de referência de baixa extremidade ofMais baixo | Entrada de sinal habilitada para dígitos de 8 bits, este pino é o pino de entrada lógica deofcontrole de data gating, sua função é realizar o controle de três estados |

|  |

| externamente nos dados de saída de 8 bits inferiores do conversor. O nível baixo é | válido, os dados de saída de 8 bits inferiores do conversor ocupam os dados |

estado de resistência e o dispositivo não ocupa o barramento de dados. Habilitare o tempo de atraso de liberação é de 600ns (máximo). | superior | Entrada de sinal habilitada para dígitos de 8 bits, este pino é o pino de entrada lógica de | controle de data gating, sua função é realizar o controle de três estados | externamente nos dados de saída de 8 bits superiores do conversor. Nível baixo | é válido, os dados de saída de 8 bits mais altos do conversor ocupam obarramento de dados; Em alto nível, o pino de dados de saída de 8 bits mais altos está em alta | estado de resistência e o dispositivo não ocupa o barramento de dados. Habilitar | e o tempo de atraso de liberação é de 600ns (máximo). | Inibir estática |

entrada de sinal, este pino é o pino de entrada da lógica de controle, sua função | é a saída de dados externamente para o conversor para realizar opcional | Nitravamento ou controle de desvio. Em alto nível, os dados de saída do | o conversor produz diretamente sem travamento; em nível baixo, a saída | dados do conversor estão travados, os dados não são atualizados, mas oloop interno não é interrompido, e o rastreamento está operando todo o | tempo, Inhibit conectou resistência de pull-up internamente. Após 600ns (máx.) de atraso de | Au borda descendente do sinal estático, os dados se tornam estáveis (se o | dispositivo ocupa o barramento de dados, ou seja, quando ele emite os dados dependesobre o estado de | eSaída do sinal CB “Ocupado”, este sinal indica se o código binário |

X

X