| Sistema completo de 2 velocidades |  |

| Relações de velocidade programáveis em canal grosso/fino | |

| 1:8, 1:16, 1:32, 1:64 | |

| Saída digital com travas de 3 estados | |

| A resolução máxima é de 20 bits | |

| A precisão máxima é de 5 Arcsec |

| contêm sincronização bidirecional grossa/fina para conversores digitais ou resolver para |

|

| conversores digitais e circuito lógico corretor de erros exigido por dois |

As relações de velocidade da combinação grossa/fina dos produtos da Série HTS20 são | 1:8, 1:16, 1:32, 1:64,a relação de velocidade necessária pode ser obtida por | programa externo. É conveniente de usar. Entrada grossa/fina bidirecional sinais são sinais de sincronismo de três fios ou resolver de quatro fios. Saída do conversor SDC/RDC programável de 2 velocidades da série HTS20 natural | códigos binários paralelos. O máximo é de até 20 bits. Eles têm 3 estados | travas. | |

4 ESPECIFICAÇÕES TÉCNICAS de Conversores Sincro para Digital ou | Resolvedor para conversores digitais Série HTS20 SDC/RDC programável de 2 velocidades | ||||

Conversores (Aba 2, Aba 3) | Tabela 2 Condições nominais e condições operacionais recomendadas * significa que pode ser feito sob encomenda. Tabela 3 Características elétricas Características Condições | - - - - | 17 18 19 20 | HTS20R/HTS20S | |

Padrão militar de negócios | (Q/HW30925-2006) Unidades Comentários Mín. Máx. | - - - - | 40 20 10 5 | Resolução | |

(opcionalmente controlado por SC1, SC2) Relação de velocidade 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 pedaço 90 | Precisão (0°~360°) Hz V V | |

|  |

10k 115 | |

,

, Resolvedor para conversores digitais Série HTS20 SDC/RDC programável de 2 velocidades

Resolvedor para conversores digitais Série HTS20 SDC/RDC programável de 2 velocidades Conversores (Fig 2, Fig 3)

Conversores (Fig 2, Fig 3) ,

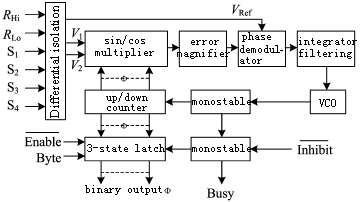

, (1) Conversor de velocidade única

(1) Conversor de velocidade única Os princípios de operação do conversor de velocidade única são mostrados na fig2., os princípios são resumidos da seguinte forma:

Os princípios de operação do conversor de velocidade única são mostrados na fig2., os princípios são resumidos da seguinte forma: Onde θ é o ângulo de entrada analógico.

Onde θ é o ângulo de entrada analógico. ,

, Os dois sinais são multiplicados pelo ângulo digital φ de subida/descida interna

Os dois sinais são multiplicados pelo ângulo digital φ de subida/descida interna .

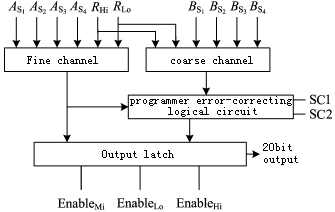

.Os princípios de operação do conversor de 2 velocidades são mostrados na fig3. o | operação do canal grosso e fino do conversor de 2 velocidades é o |

|  |

| igual à velocidade única acima mencionada, mas o conversor de 2 velocidades consiste em dois conjuntos de conversor de velocidade única e erro lógico do programador o circuito. O canal grosseiro cumpre a conversão do ângulo lógico de 10 ~ 12 bits | |

ângulo para ângulo digital. ângulos digitais convertidos pelo canal Coarse e | Os canais finos são inseridos na lógica de correção de erros do programador | circuito respectivamente. Após o processamento e correção do erro, ele | saída de um dígito binário paralelo de 20 bits, que é inserido na saída | trava e buffer para saída de ângulo digital, cumprindo toda a | conversão. | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Figura 2 Diagrama de bloco funcional Figura 3 Diagrama de bloco funcional do conversor de velocidade única do conversor de 2 velocidades (3) Método e tempo de transferência de dados As saídas dos conversores de 2 velocidades da série HTS20 atingem 20 bits. Através e que assumem o controle de 3 estados da trava de saída, o conversor de 2 velocidades pode ser facilmente conectado ao barramento de dados. e T1 T2 são todos válidos em nível baixo. EnableLo controla 8 bits baixos, EnableMi controla 8 bits médios, controles EnableHi descansam bits altos. Os dados dos conversores de 2 velocidades da série HTS20 são lidos da seguinte forma: Definir para “0” lógico, após 490μm, os dados no latch de 3 estados do conversor são atualizado. Pode ler dados de 8 bits baixos, 8 bits médios e bits altos através do controle e Figura 4 Fornece o tempo de leitura de dados quando o conversor de 2 velocidades e o barramento de dados de 8 bits estão conectados. Para garantir a conversão de alta precisão do conversor de 2 velocidades, preste atenção ao seguinte:

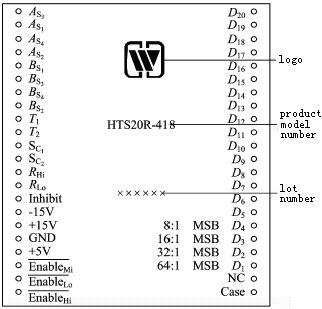

| As amplitudes dos sinais de entrada dos canais grossos e finos devem ser garantidas dentro do valor nominal de 10%. As frequências dos sinais de entrada e os sinais de referência dos canais grosseiros e finos devem ser as frequências de operação especificadas. Deslocamento de fase entre o sinal de entrada e o sinal de referência de grosseiro canal e fase entre o sinal de entrada e o sinal de referência de multa canal deve ser inferior a 10°. Distorções de onda de sinais de entrada e sinais de referência de canais grossos e finos devem ser inferiores a 5%. A variação da fonte de alimentação de +5V, ±15V deve ser garantida dentro de ±5%. 6 DIAGRAMA MTBF de Conversores Sincro para Digital ou Resolvedor para conversores digitais Série HTS20 SDC/RDC programável de 2 velocidades Conversores (Fig. 5) 7 CONFIGURAÇÕES DE PIN de Conversores Sincro para Digital ou Resolvedor para conversores digitais Série HTS20 SDC/RDC programável de 2 velocidades Conversores (Fig6, Tab4) Figura 5 MTBF vs. temperatura Figura 6 Pin out view superior (Nota: De acordo com GJB/Z 299B-98, assumindo esse terreno está em boas condições) Tabela 4 Descrição do pino Alfinete Mnemônico Descrição Alfinete Mnemônico Descrição As3 As1 As4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | As2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RHi RLo Inibir -15V +15V GND +5V Entrada de canal fino Entrada de canal fino | Entrada de canal fino Entrada de canal fino Entrada de canal grosso Entrada de canal grosso Entrada de canal grosso Entrada de canal grosso Pino de ajuste para mudança de fase entre sinal e referência Pino de ajuste para mudança de fase entre sinal e referência Pino de controle de programa para grosso e taxas de velocidade finas Pino de controle de programa para grosso e taxas de velocidade finas Pino de entrada para referência alta Pino de entrada para referência baixa Sinal de inibição -15V entrada +15V entrada terra entrada +5V habilitar dados médios de 8 bits | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

Não conectado Saída do ângulo digital combinado mais alto | Saída de ângulo digital combinado | Saída de ângulo digital combinado Saída de ângulo digital combinado | Saída de ângulo digital combinado | Saída de ângulo digital combinado Saída de ângulo digital combinado | Saída de ângulo digital combinado |

Saída de ângulo digital combinado | Saída de ângulo digital combinado | 8 | Saída de ângulo digital combinado | 15 | Saída de ângulo digital combinado |

2 | Saída de ângulo digital combinado | 9 | Saída de ângulo digital combinado | 16 | Saída de ângulo digital combinado |

3 | Saída de ângulo digital combinado | 10 | Saída de ângulo digital combinado | 17 | Saída de ângulo digital combinado |

4 | Saída de ângulo digital combinado | 11 | Saída do ângulo digital menos combinado | 18 | Observação: |

5 | Os pinos 3,7 do HTS20S não estão conectados. | 12 | As1,As2, As3, As4 são entradas de canal finas. Se o sincronismo estiver equipado com três fios, o As4 não será usado. | 19 | Bs1,Bs2,Bs3,Bs4 são entradas de canal grosseiro. Se o sincronismo estiver equipado com três fios, Bs4 não será usado. |

6 | RHi, RLo são entradas de sinal de referência. | 13 | Inibir é o sinal de inibição que é conectado à fonte de alimentação de 5V por resistor de pull-up. Quando Inhibit é lógico “0”, dentro é inibido. Após 490ns, os dados válidos são emitidos e podem ser lidos. Quando é lógico "1", o conversor restaura o estado de rastreamento, os dados de saída são dados inválidos. | 20 | Inibir |

7 | e | 14 | são três pinos de controle de estado de saída de dados, que determinaram o estado |

A caixa é o pino da caixa.

D1~D20 são Saídas de ângulo digital combinado. D20 é menos significativo

pedaço. Quando a relação de velocidade é 1:8, D4 é o bit mais significativo. Quando a velocidade | proporção é 1:16, D3 é o bit mais significativo. Quando a relação de velocidade é 1:32, D2 | é o bit mais significativo. Quando a relação de velocidade é 1:64, D1 é mais | bit significativo. TABELA DE PESO DE 8 BITS de conversores ou resolvedores de sincronização para digital | para Conversores Digitais Série HTS20 SDC ou RDC de 2 velocidades programáveis Conversores (Aba 5) | Tabela 5 Tabela de peso de bits | Pedaço | número Peso (graus) | Pedaço |

número | Peso (graus) Pedaço | número | Peso (graus) | 1 (MSB) | 180.0000 1,1063 | 0,011(40s) | 90.0000 |

|

|

| 45.0000 |

X

X