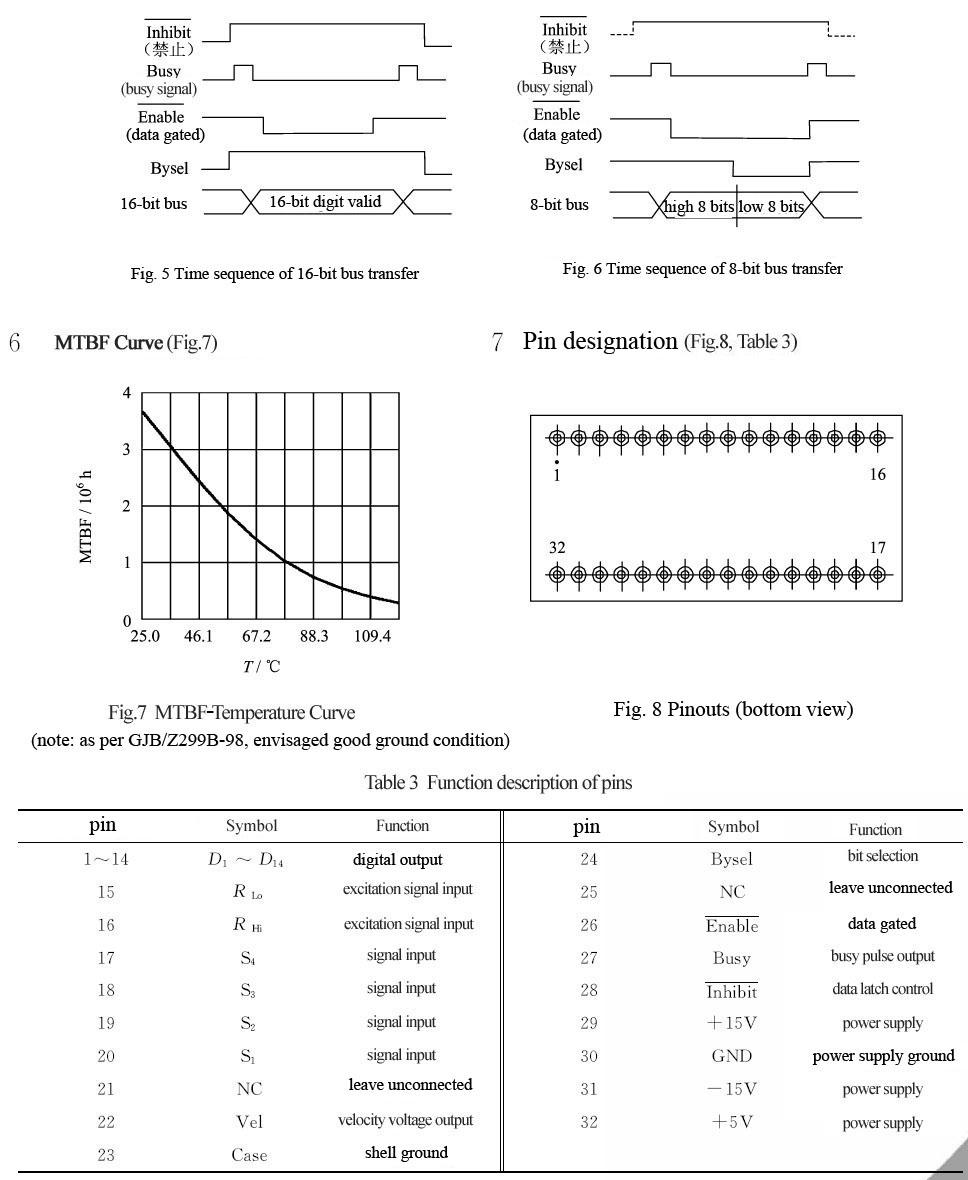

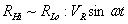

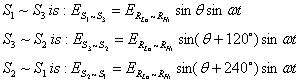

A potência de operação adota ±15V e + 5V DC. Existem dois tipos de sinal de saída: sincronismo de três linhas e sinal de referência (conversor SDC) ou resolver e sinal de referência de quatro linhas (conversor RDC); a saída adota códigos digitais paralelos do sistema binário.

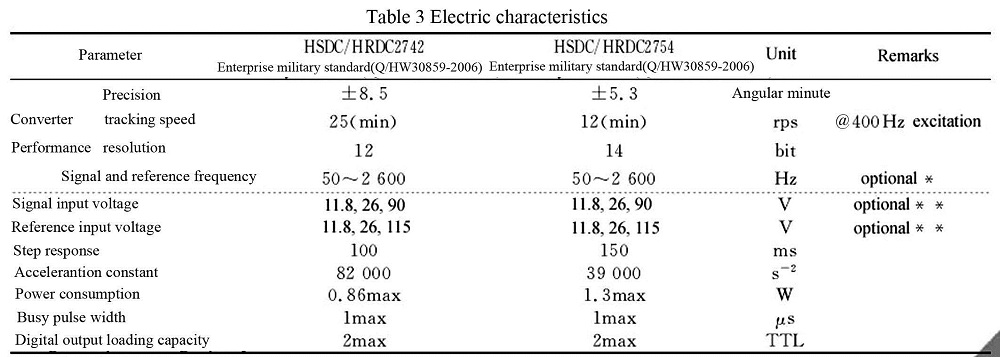

| Resolução: 12 bits, 14 bits |  |

| Alta velocidade de rastreamento | |

| Integração híbrida, gabinete de metal | |

| Saída de trava de três estados | |

| Com sinal de velocidade saída Vel | |

| Compatibilidade indefinida com a série AD1740 |

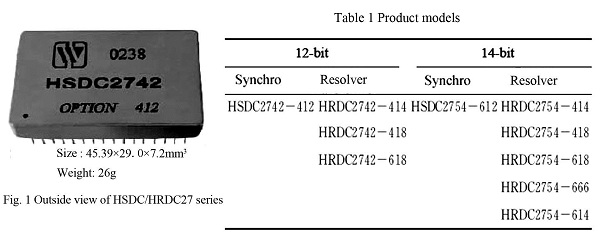

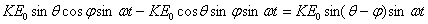

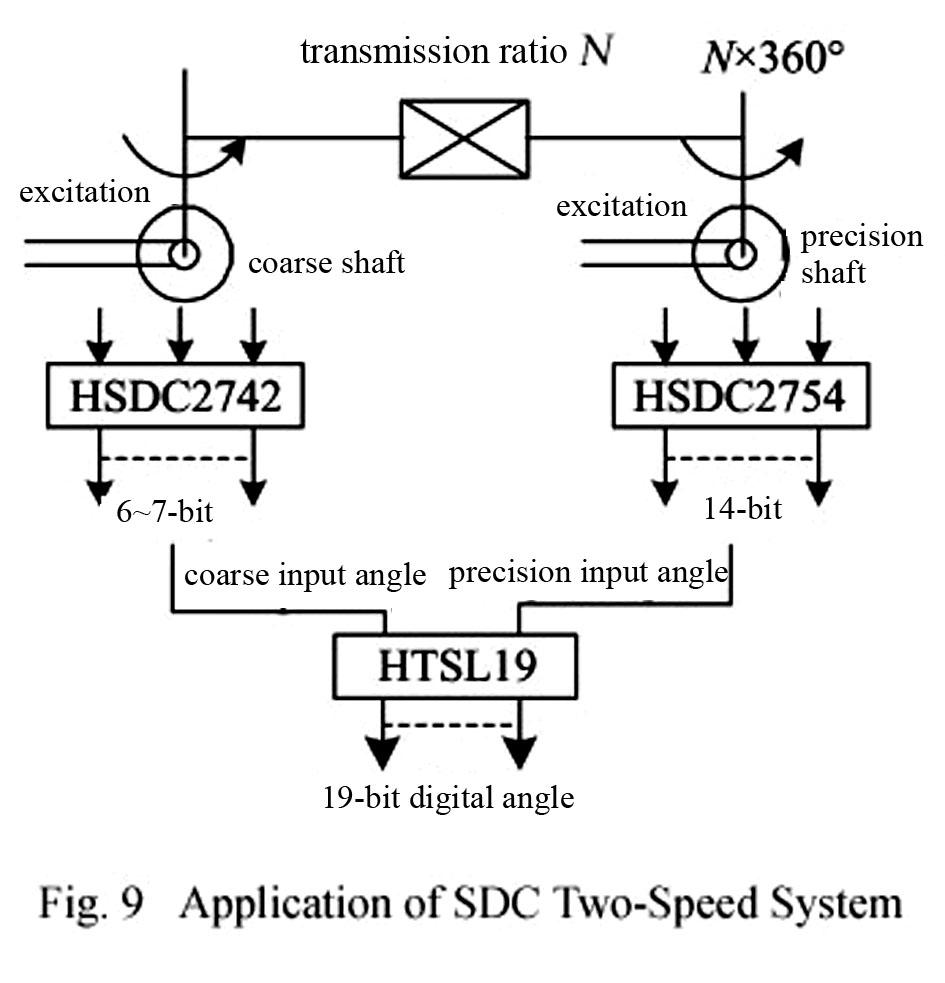

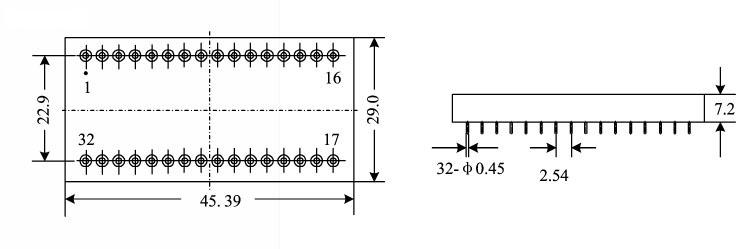

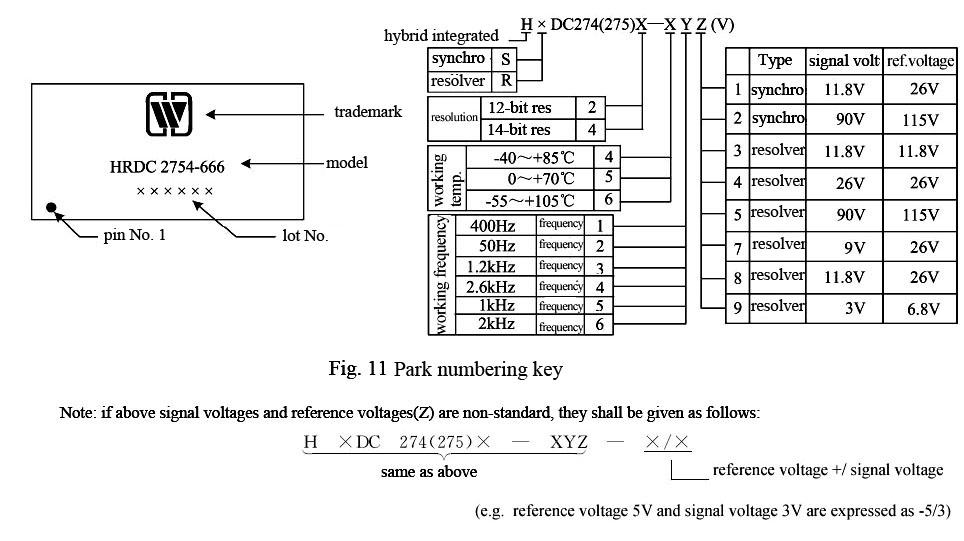

A série HSDC/HRDC27 é o conversor digital para sincronizador ou resolvedor para conversor digital para rastreamento contínuo do loop servo tipo II, trava e emite paralelamente dados codificados binários naturais de 12 ou 14 bits com metal dual-in-line de 32 linhas pacote, apresenta as vantagens de pequeno volume, peso leve e alta confiabilidade etc., é amplamente aplicado em tal sistema de controle automático como sistema de radar, sistema de navegação, etc.

A potência de operação adota ±15V e + 5V DC. Existem dois tipos de sinal de saída: sincronismo de três linhas e sinal de referência (conversor SDC) ou resolver e sinal de referência de quatro linhas (conversor RDC); a saída adota códigos digitais paralelos do sistema binário.

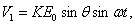

Tabela 2 Condições nominais e condições operacionais recomendadas

Absoluto máx. Valor nominal | Tensão de alimentação Vs: ± 17,5 V |

Tensão lógica VL: +5,5V | |

Faixa de temperatura de armazenamento: -55℃~+125℃ | |

Condições de operação recomendadas | Tensão de alimentação Vs: ± 5V |

Tensão lógica VL: 5V | |

Valor efetivo da tensão de referência VRef: ±10% do valor nominal | |

Validade da tensão do sinal V1*: ±5% do valor nominal | |

Frequência de referência f*: 50Hz~2,6kHz | |

Faixa de temperatura operacional TA: -40~+85℃,-55~+105℃ |

Observação: * indica que pode ser personalizado conforme requisito do usuário.

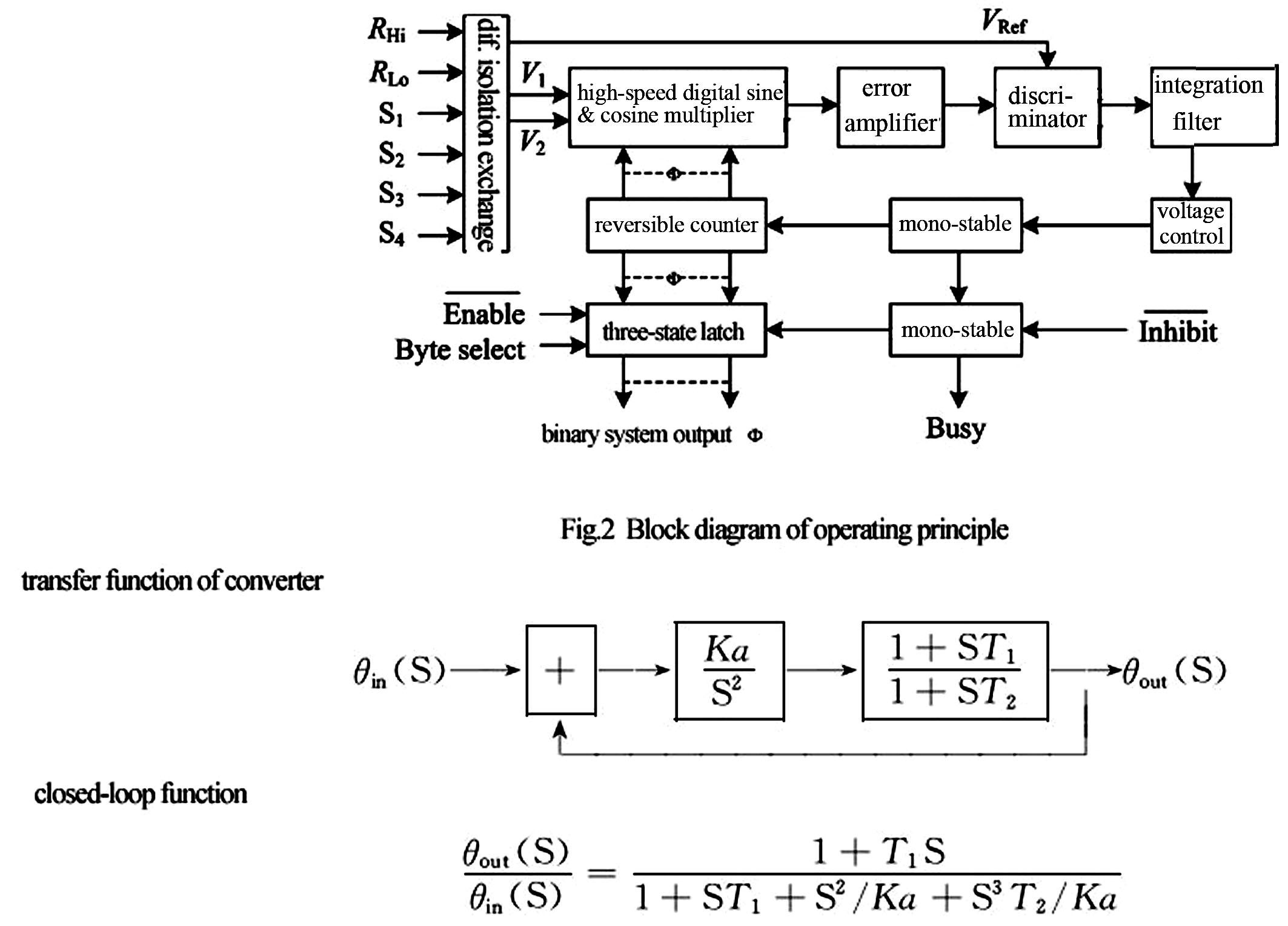

| saída; ler dados de 12 ou 14 bits; defina Inibir para lógico "1" para |  |

| transferência de 16 bits). | B: o conversor está conectado ao barramento de 8 bits, o bit D1~D8 está conectado ao barramento de dados e o restante está vazio. |

| |

| Inibir é | |

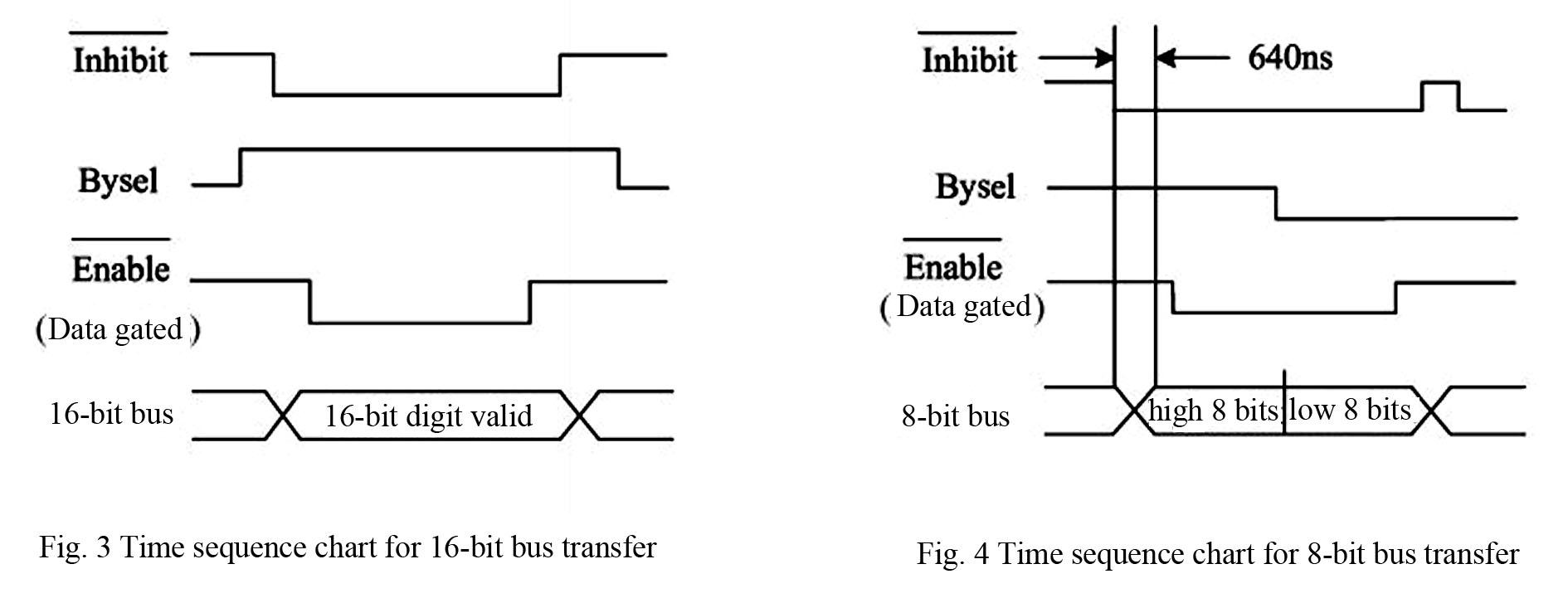

| Habilite para lógico “0”, os dados do latch dentro do conversor podem | ser saída; se Byse1 estiver configurado para lógico “1”, o conversor lê diretamente | os dados de 8 bits mais altos, se Byse1 for definido como lógico “0”, o conversor lê | os bits restantes, adicionam automaticamente zero para bits incompletos; defina o controle de bloqueio de dados de inibição (sinal de inibição) para a lógica "1" para se preparar para a leitura dos próximos dados válidos (consulte a Fig. 3 e a Fig. 4 para a sequência de tempo de transferência de 8 bits) | (2) Método ocupado (leitura assíncrona): | No modo de leitura assíncrona, o controle de bloqueio de dados de inibição (sinal de inibição) é definido como lógico "1" ou vazio, independentemente de o loop interno estar sempre em | o estado estável ou se os dados de saída são válidos deve ser determinado | através do estado de sinal de ocupado Ocupado. Quando o sinal de ocupado está alto | nível, indica que os dados estão sendo convertidos e os dados neste |

| o tempo é instável e inválido; quando o sinal de ocupado está em nível baixo, | indica que a conversão de dados foi concluída e os dados neste | Au | o tempo é estável e válido. Uma vez que o nível alto ocorre em Ocupado durante a leitura, | Au | a leitura deste tempo é inválida. No modo de leitura assíncrona, Ocupado | Au | saída é trem de pulso do nível TTL, a largura entre está relacionada a | velocidade de rotação. Da mesma forma, também existem dois usos de 8 bits e 16 bits |

X

X